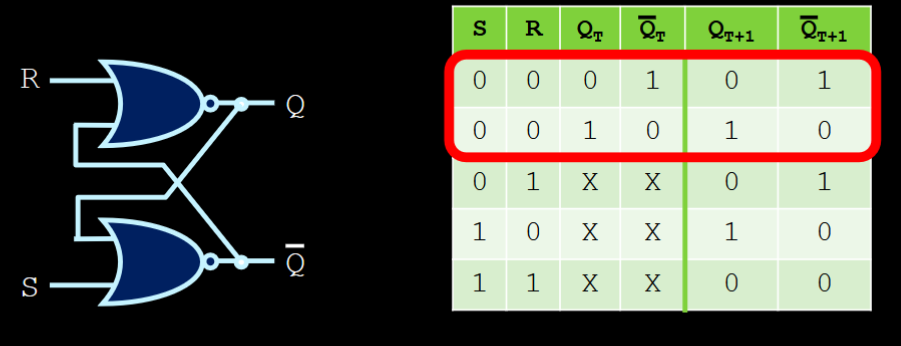

latches

represents “SET” and represents “RESET”

- Recall from Intuition Behind Storing Values, for a NAND gate, when A=0, the output must be 1. A 0 input locks the NAND gate

- When then will be 1 no matter what!

- When then will be 1 no matter what!

However, in the case where and are 0, the and haven’t really settled on a value. The output becomes 1, 1, which is forbidden because it makes no sense.

- When , this is a forbidden state

Essentially with S = R = 1, that is your forbidden state for any latch. Also, implies no change happens; things hold their data

Race Condition

Going from 00 to 11 results in a race condition where whichever input is “inputted” first decides which of the last 2 rows in the chart given does the output assume.

- Whichever gets received first depends on gate delays and RNG

SR Latch

- R and S retain their meaning clearer. Also S=R=1 is a forbidden state.

- We have unstable behaviour when going from 11 to 00

- Otherwise similar to the other latch