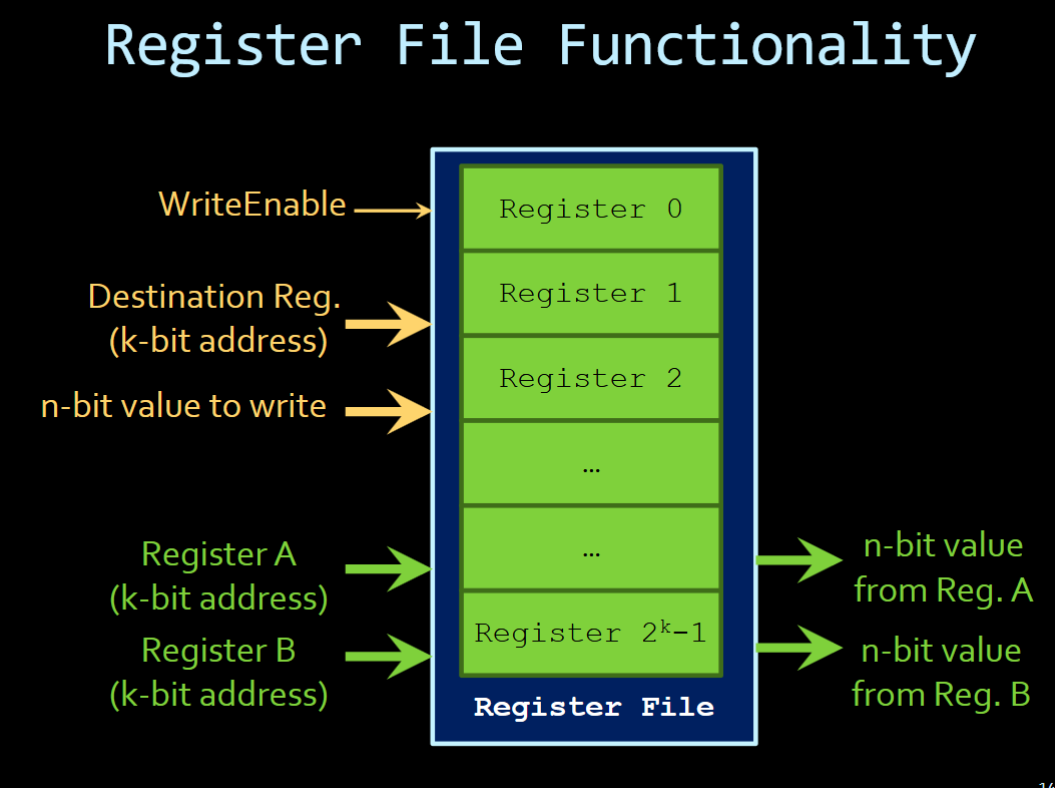

A small number of fast memory units Lets multiple values be read and written simultaneously (wait whattodo)

- A collection/array of registers

- Each register has an address (a number for the register)

- Depending on the total number of address bits we can handle for reading or writing, say

k, then we can have at most2^kregisters!- i.e. if k is 5 bits, you can store 32 registers

- Each register also has a certain

n-bit width (i.e. each register can holdn-bits of info)- Each register might be 64 bits in, say, x86-64

- In MIPS it’s

32bits!

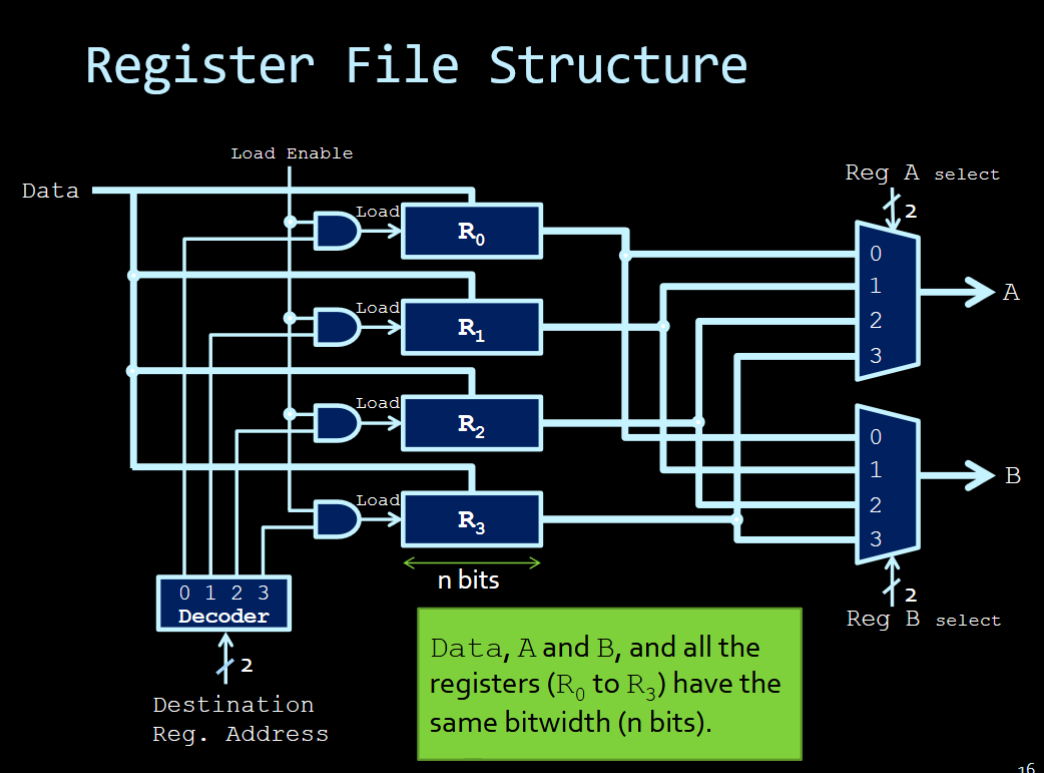

Functionality

- We can read two registers with this implementation! Register A and B draw from the

Qoutputs of all registers and uses a one-hot decoder to get the selected output. This results inn-bit outputs - For writing we have a

nbit input to override a register’s data with. - For writing we also have a

kbit input as well. This is ourDestination Reg. - To know if we are writing we have a

WriteEnableinput. We don’t need aReadEnablebecause we can just decide not to read the data… Reading is trivial. You pass in

Reading is trivial. You pass in kbits and that represents the address. You can decode that to select the right register’s outputQand output that. Double that for A and B to read many data simultaneously

As for writing you need write enable true. The destination register address is decoded to enable writing for the specific register. We want to load when WriteEnable and the decoder agree on a register, so we need k AND gates as well. Then the n bit input, passed into all registers, finally gets to change the register value.