A larger than Register File grid of slower memory cells Stores most info to be processed by the CPU (Almost like a 2D array)

Problem: We can’t store 1 billion registers with a register file!

- I.e a phone can store a billion 32-bit numbers!

- Too many wires and flip flops; each flip flop has too many gates

RAM! (Main Memory)

- Main Memory is a collection of addressable memory units

- Each cell is in units of bytes

- bytes = 8 bits

- A word is 4 “sections in memory” or 4 bytes.

- For us, a word is 4 bytes / 32 bits

- Like a register file

- You have at most

2^mrows wheremis the bit-length of the address you’re passing. - Each row is

nbits.- So the size of memory is

2^m * nbits in total

- So the size of memory is

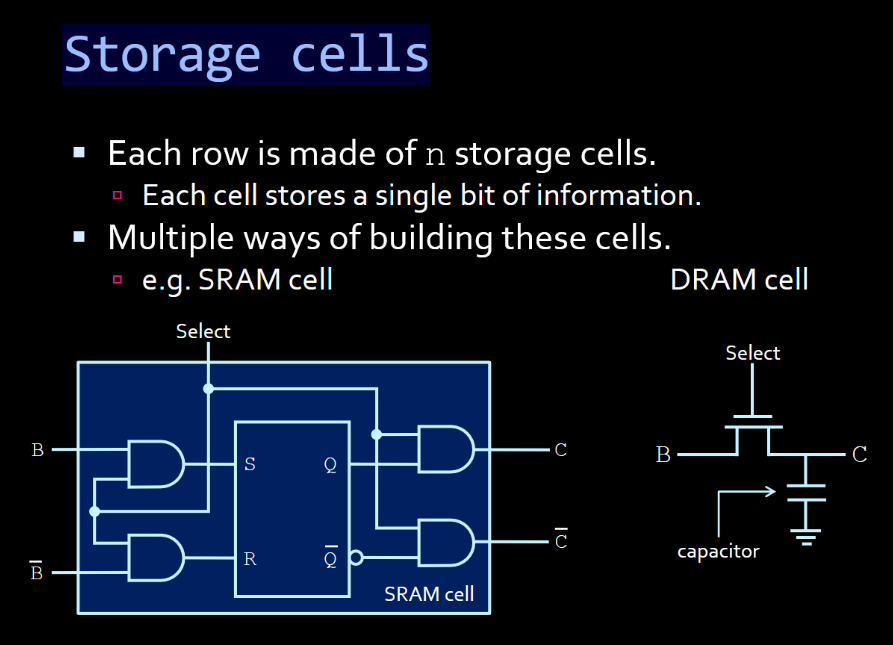

- Different from a register file cuz instead of an array of registers, we have rows of memory units / storage cells

- DRAM cells are for big memory cuz they are so tiny

- SRAM is fast tho

Organization

- For this example assume

n=3even though it’s not very practical. Usually it’sn=8(a byte)- Usually 4 of the 8 bit rows are accessed as

wordsas we defined above

- Usually 4 of the 8 bit rows are accessed as

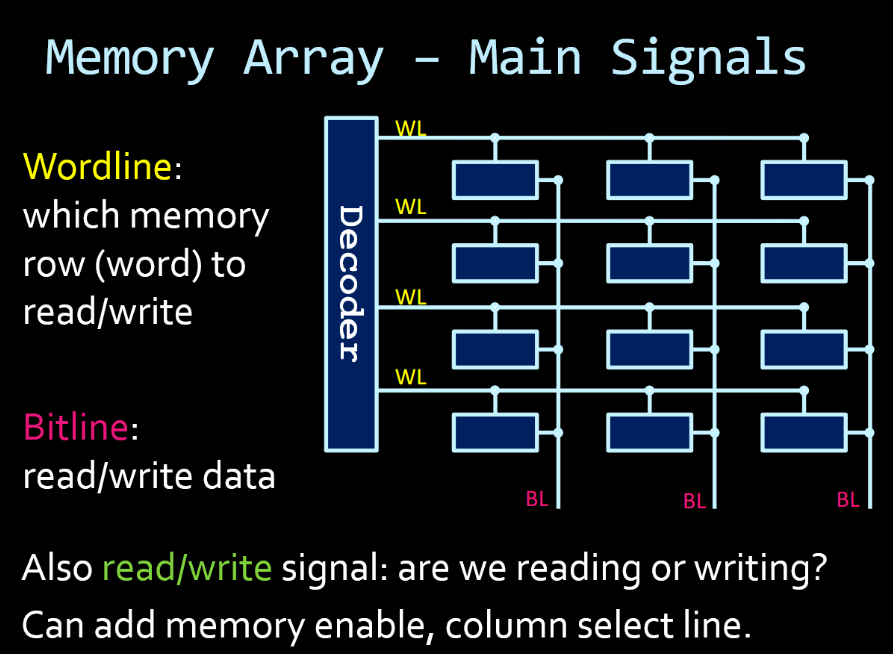

- Anyway the wordline determines which row (a byte, 8 bits, in MIPS, that we we are reading from)

- The bitline is attached to the cells of the wordlines and sends them to their output all nicely.

- Cells by default output 0 when the wordline connected is inactive (refer to the diagrams above), but if a wordline is active and a cell outputs

1into the bitline connected already to0, we get a short circuit.- Solution? Data Bus

- If we want to read from the cell, we pull, from the bits into the bitline, through a tri-state buffer

- If reading, we set

ENfor the buffer to true such that everything else is disconnected = no short circuit!

- If reading, we set